Derive the state diagram and state table for the circuit. All the states are required there is no need to build reset circuit. asynchronous up down counter design.

Asynchronous Up Down Counter Design, Here T Flip Flop is used. As we know that in the up-counter each flip-flop is triggered by the normal output of the preceding flip-flop from output Q of first flip-flop to clock of next flip-flop. In certain applications a counter must be able to count both up and down.

2 Bit Comparator 2 Bits Logic Digital Circuit From pinterest.com

2 Bit Comparator 2 Bits Logic Digital Circuit From pinterest.com

That is if 0 is given as the input 1 is produced at the output and vice versa. 1 Now i want to swap the 2 differential inputs so that it can count down. HelloHere i explained how to design asynchronous updown counterThanks for watchingwatch my other videos alsoMy videosImportant days in June for the competi.

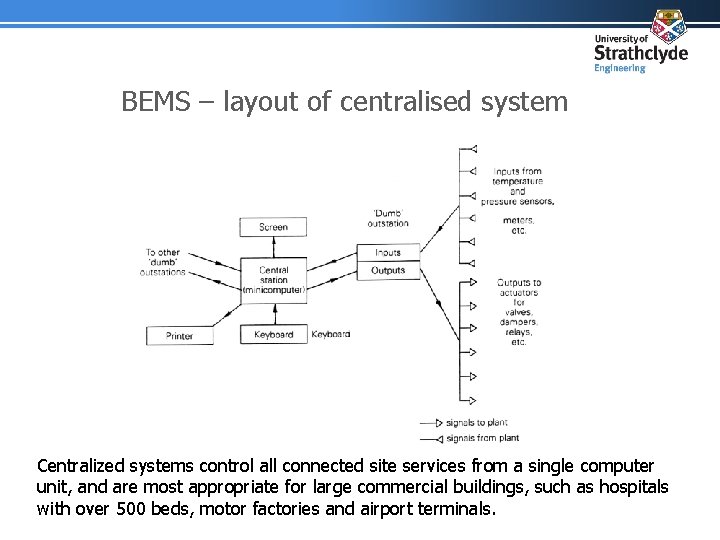

The circuit below is a 3-bit up-down counter.

Asynchronous counters can be easily built using Type D flip-flops. The block diagram of 3-bit Asynchronous binary down counter is similar to the block diagram of 3-bit Asynchronous binary up counter. Both up and down counters are designed using the asynchronous based on clock signal we dont use them widely because of their unreliability at high clock speeds. ASYNCHRONOUS UP DOWN COUNTER. Asynchronous or ripple counters. I have designed the circuitIt counts up during ive cycle.

Another Article :

In this a mode control input say M is used for selecting up and down mode. HelloHere i explained how to design asynchronous updown counterThanks for watchingwatch my other videos alsoMy videosImportant days in June for the competi. Counters are of two types. Steps to design Synchronous 3 bit UpDown Counter. 8 clever moves when you have 1000 in the bank. Design 2 Bit Synchronous Up Down Counter Using T Flip Flop Bits Flop Design.

Synchronous counter has its flip-flops clocked at the same time whilst asynchronous counter is not. In other words this flip-flop produces complementing output. Since it is MOD-8 counter 3 T flip-flop are required. Digital Logic AND Gate. Whereas for the up-down counter you can use multiplexers as switches as we saw in the design of the 3-bit synchronous up-down counter. Binary To Excess 3 Code Converter 3 Bit Coding Binary Converter.

As we know that in the up-counter each flip-flop is triggered by the normal output of the preceding flip-flop from output Q of first flip-flop to clock of next flip-flop. Asynchronous counters are used in Mod N ripple counters. You may also read. 0 3 2 1 0 3 2 1 etc. Design of 3 bit Asynchronous updown counter. 4 Bit Parallel Subtractor Parallel Logic Design.

Digital Logic AND Gate. Synchronous counter has its flip-flops clocked at the same time whilst asynchronous counter is not. Design A Modulo 5 Synchronous Counter State Diagram We Note That Will Require 3 Flip Flops To Implement This Circuit As There Are 8 Possible States Of The Three Not Be Assigned Perhaps Should Consider What Happens If. They are used in designing asynchronous decade counter. Since it is MOD-8 counter 3 T flip-flop are required. Pin On Digital Electronics Circuits.

Whereas in a down-counter each flip-flop is triggered by the complement output of the preceding flip-flop from output Q of first flip-flop to clock of. The clock inputs of all flip flops are cascaded and the D input DATA input of each flip flop is connected to logic 1. Written 49 years ago by navyanagpal99 180. In an asynchronous counter all the clock inputs of the flip-flops have a unique input that is not shared with any other flip-flop in the system. Asynchronous Binary Down Counter. Design A 2 Bit Synchronous Down Counter Using T Flip Flop Post Design Counter 2 Bits.

Written 49 years ago by navyanagpal99 180. Circuit design Asynchronous up down counter created by T V R TRIVEDHI with Tinkercad. Design of Synchronous Counters. The clock of the preceeding flip-flop of the. Synchronous counter has its flip-flops clocked at the same time whilst asynchronous counter is not. 4 Bit Asynchronous Up Down Counter Counter Electronics Circuit Logic.

They are used in designing asynchronous decade counter. For a 4-bit counter the range of the count is 0000 to 1111. As we know that in the up-counter each flip-flop is triggered by the normal output of the preceding flip-flop from output Q of first flip-flop to clock of next flip-flop. It is also used in Ring counter and Johnson counter. How Asynchronous 3-bit up down counter construct. Pin On Digital Electronics Circuits.

As we know that in the up-counter each flip-flop is triggered by the normal output of the preceding flip-flop from output Q of first flip-flop to clock of next flip-flop. It is simple modification of the UP counter. In an asynchronous counter all the clock inputs of the flip-flops have a unique input that is not shared with any other flip-flop in the system. Both up and down counters are designed using the asynchronous based on clock signal we dont use them widely because of their unreliability at high clock speeds. All the states are required there is no need to build reset circuit. 2 Bit Synchronous Down Counter Electronics Circuit Counter Digital.

Another disadvantage of the asynchronous or ripple counter circuit is limited speed. That is if 0 is given as the input 1 is produced at the output and vice versa. The asynchronous counter is also called a ripple counter. Notice that an asynchronous up-down counter is slower than an up counter or a down counter because of the additional propagation delay introduced by the NAND networks. I have to design a counter with 2 differential inputsIt should count up in ive clock and count down during -ive clock cycleAlso it should shift the count serially. 3 Bit Synchronous Up Down Counter Counter Electronics Circuit Digital.

Asynchronous or ripple counters. Design A Modulo 5 Synchronous Counter State Diagram We Note That Will Require 3 Flip Flops To Implement This Circuit As There Are 8 Possible States Of The Three Not Be Assigned Perhaps Should Consider What Happens If. If X 1 the device counts down. I have to design a counter with 2 differential inputsIt should count up in ive clock and count down during -ive clock cycleAlso it should shift the count serially. It counts from 2 𝑁 1 to 0. 2 Bit Comparator 2 Bits Logic Digital Circuit.

They can be implemented using divide by n counter circuit which offers much more flexibility on larger counting range related applications and the truncated counter can produce any modulus number count. How Asynchronous 3-bit up down counter construct. 2 I dont know how to shift this data serially. Solved C An Asynchronous Mod 8 Counting Up Circuit Using Chegg Com. You may also read. 3 Bit Multiplier In 2021 Logic Design Circuit Digital.

How Asynchronous 3-bit up down counter construct. In this a mode control input say M is used for selecting up and down mode. Notice that an asynchronous up-down counter is slower than an up counter or a down counter because of the additional propagation delay introduced by the NAND networks. What is clock ripple. For n 3 ie for 3 bit counter Maximum count 2 n -1 and number of states. Binary To Gray Code Converter 4 Bit In 2021 Coding Binary Converter.

Asynchronous or ripple counters. That is if 0 is given as the input 1 is produced at the output and vice versa. For a 4-bit counter the range of the count is 0000 to 1111. 1 Now i want to swap the 2 differential inputs so that it can count down. Here we are performing 3 bit or mod-8 Up or Down counting so 3 Flip Flops are required which can count up to 2 3 -1 7. 4 Bit Asynchronous Up Down Counter Counter Electronics Circuit Logic.

Design A Modulo 5 Synchronous Counter State Diagram We Note That Will Require 3 Flip Flops To Implement This Circuit As There Are 8 Possible States Of The Three Not Be Assigned Perhaps Should Consider What Happens If. Note two transitions between the state pairs. The MOD of the ripple counter or asynchronous counter is 2n if n flip-flops are used. But despite those features Asynchronous counter offer some limitations and. If X 1 the device counts down. Demultiplexer Using Logic Gates Circuit Design Electronics Circuit Logic.

Because the output toggles in T flip-flop. In this a mode control input say M is used for selecting up and down mode. The block diagram of 3-bit Asynchronous binary down counter is shown in the following figure. If X 1 the device counts down. For the design of the asynchronous counter T flip-flops are used. Piso Shift Register Shift Register Shift Electronics Circuit.